# X-Band MMIC Power Amplifier With an On-Chip Temperature-Compensation Circuit

Kazuhisa Yamauchi, *Member, IEEE*, Yoshitada Iyama, *Member, IEEE*, Mamiko Yamaguchi, Yukio Ikeda, *Member, IEEE*, Shuji Urasaki, *Senior Member, IEEE*, and Tadashi Takagi, *Member, IEEE*

**Abstract**—An *X*-band monolithic-microwave integrated-circuit (MMIC) power amplifier with a simplified on-chip temperature-compensation circuit composed of a few diodes and a resistor are presented in this paper. At first, the operation principle and design method of the temperature-compensation circuit have been investigated. The fabricated four-stage *X*-band MMIC power amplifier with the on-chip temperature-compensation circuit has demonstrated the improvement of gain variation from 5.5 to 1.3 dB in the temperature range from  $-10^{\circ}\text{C}$  to  $+80^{\circ}\text{C}$ .

**Index Terms**—Gain control, MMIC power amplifiers, Schottky diodes, temperature control.

## I. INTRODUCTION

**I**N RECENT years, there have been increasing demands for power amplifiers with small gain variation with temperature. However, it is known that multistage FET amplifiers are seriously affected by temperature variation, resulting in a gain spread of several decibels for amplifiers. It is known that the compensation of gain variation for FET amplifiers can be realized by controlling drain currents and input power levels; a design method which uses an off-chip regulator [1] or an attenuator [2], [3] with a temperature sensor in the module. As a result, the module becomes larger. The preferable design solution for realizing miniaturization of modules has been considered to employ amplifiers with an on-chip temperature-compensation circuit [4], [5]. They control the gate voltage of the FET in order to obtain the constant drain current with temperature, which may compensate the gain of the FET with temperature. However, they cannot achieve optimal gain compensation with temperature. Moreover, they require a series resistance in the drain-bias circuit to monitor the drain current, which leads to a significant voltage drop for power amplifiers.

To address these problems of conventional technologies, we present a simplified on-chip temperature-compensation circuit, which consists of only a few diodes and a resistor. The presented compensation circuit controls the gate voltage in order to keep the gain constant with temperature. The presented compensation circuit utilizes the mechanism that the threshold voltage of a diode decreases with the increasing of temperature. In this

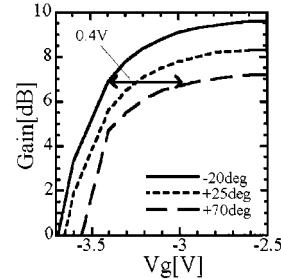

Fig. 1. Measured gain characteristics of a single-stage amplifier, which employs a GaAs MESFET with a gatewidth of  $900\ \mu\text{m}$  at  $V_{\text{ds}} = 5\ \text{V}$  at the center frequency.

paper, at first, the operation principle and design method of the temperature-compensation circuit have been investigated. We have developed a four-stage *X*-band monolithic-microwave integrated-circuit (MMIC) power amplifier with the presented on-chip temperature-compensation circuit. The fabricated amplifier has demonstrated an improvement of gain variation from 5.5 to 1.3 dB in the temperature range from  $-10^{\circ}\text{C}$  to  $+80^{\circ}\text{C}$ .

## II. GAIN CHARACTERISTICS DEPENDING ON TEMPERATURE FOR FET AMPLIFIER

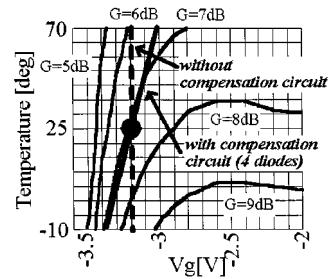

The gain of a GaAs FET amplifier decreases with the increase of temperature, while the gain of the FET amplifier operating at class AB increases with the increase of a gate voltage. To compensate the gain variation of an amplifier with temperature, controlling the gate voltage of an FET can be used. Fig. 1 shows measured gain characteristics of a single-stage amplifier at the three temperature points  $-20^{\circ}\text{C}$ ,  $+25^{\circ}\text{C}$ , and  $+70^{\circ}\text{C}$  as a function of gate voltage. From Fig. 1, it can be seen that the gain can be kept constant in the temperature range from  $-20^{\circ}\text{C}$  to  $+70^{\circ}\text{C}$  by adjusting the gate voltage of the amplifier when the gain of the amplifier is less than 7 dB. The gate voltage has to be varied from  $-3.4$  to  $-3$  V to achieve constant gain of 7 dB in the temperature range between  $-20^{\circ}\text{C}$  and  $+70^{\circ}\text{C}$ , as shown in Fig. 1.

## III. TEMPERATURE-COMPENSATION CIRCUIT

### A. Operation Principle

The gain variation against temperature of the amplifier can be compensated by increasing the gate voltage with an increase of temperature, as mentioned in Section II. In this section, the operation principle and design method of the temperature-compensation circuit, which is simply composed of a few diodes and a resistor, are investigated.

Manuscript received March 30, 2001; revised August 23, 2001.

K. Yamauchi, Y. Ikeda, S. Urasaki, and T. Takagi are with the Information Technology Research and Development Center, Mitsubishi Electric Corporation, Kamakura, Kanagawa 247, Japan (e-mail: yamakazu@isl.melco.co.jp).

Y. Iyama is with Kamakura Works, Mitsubishi Electric Corporation, Kamakura 247, Japan.

M. Yamaguchi is with Kitaitami Works, Mitsubishi Electric Corporation, Itami, Hyogo 664, Japan.

Publisher Item Identifier S 0018-9480(01)10436-9.

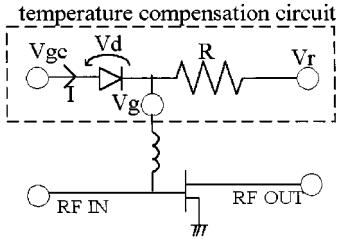

Fig. 2. Schematic diagram of the temperature-compensation circuit.

Fig. 2 shows the schematic diagram of the temperature-compensation circuit. The value of gate voltage  $V_g$  is determined by reference voltage  $V_r$  and gate control voltage  $V_{gc}$ , as shown in Fig. 2. In Fig. 2,  $I$  and  $V_d$  are the current and voltage through the diode and  $R$  is a resistor. The compensation circuit shown in Fig. 2 utilizes the decreasing threshold voltage of the diode with the increase of temperature.

In order to simplify the explanation of an operation principle, we assume  $V_{gc} = 0$ . From Fig. 2, the following equations are derived:

$$\begin{aligned} -V_r &= RI + V_d \\ I &= I_s \left\{ \exp \left( \frac{qV_d}{nkT} \right) - 1 \right\} \end{aligned} \quad (1)$$

where  $T$  and  $n$  are the temperature and an ideality factor of the diode, respectively. Here,  $I_s$  is given by the following equation as a function of temperature:

$$I_s = SA^*T^2 \exp \left( -\frac{q\phi_B}{kT} \right) \quad (2)$$

where  $A^*$  is the Richardson–Dashmann constant independent on temperature,  $\phi_B$  is the Schottky barrier voltage depending only on the material, and  $S$  is a junction size of the diode. The  $A^*$  of the  $n$ -type GaAs is  $8.1 \times 10^4 \text{ Am}^{-2}\text{K}^{-2}$ . From (1) and (2),  $V_g$  is derived as a function of  $T$

$$V_g = \left\{ \frac{kT}{q} \ln(SRA^*) + \frac{2kT}{q} \ln T - \phi_B \right\} n \quad (3)$$

where  $V_g = -V_d$ , as shown in Fig. 2, and we assume that  $RIs \ll -(V_r + V_d) \ll (1/RIs)$ . The variation of  $V_g$  with the increase of temperature is investigated. From (3), the following equation is derived:

$$\frac{\partial V_g}{\partial T} = \frac{nk}{q} \{ \ln(SRA^*) + 2 \ln T + 2 \}. \quad (4)$$

It is assumed that  $S$  and  $R$  are about  $150 \mu\text{m}^2$  and  $1 \text{ k}\Omega$ , respectively. ( $\partial V_g / \partial T > 0$ ) is then derived if  $T$  is more than  $-270^\circ\text{C}$ . We can find that  $V_g$  increases with the increase of temperature when  $T$  is more than  $-270^\circ\text{C}$ .

The variation of  $V_g$  ( $\Delta V_g$ ) between the two temperatures  $T_h$  and  $T_l$  can be calculated from following equation:

$$\begin{aligned} \Delta V_g &= \int_{T_l}^{T_h} \frac{\partial V_g}{\partial T} dT \\ &= \int_{T_l}^{T_h} \frac{nk}{q} \{ \ln(SRA^*) + 2 \ln T + 2 \} dT \\ &= \frac{nk}{q} (T_h - T_l) \ln(SRA^*) + \frac{2nk}{q} (T_h \ln T_h - T_l \ln T_l). \end{aligned} \quad (5)$$

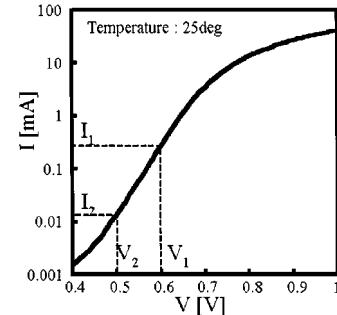

Fig. 3. Measured  $I$ – $V$  characteristics of the diode with  $S = 150 \mu\text{m}^2$  at  $25^\circ\text{C}$ .

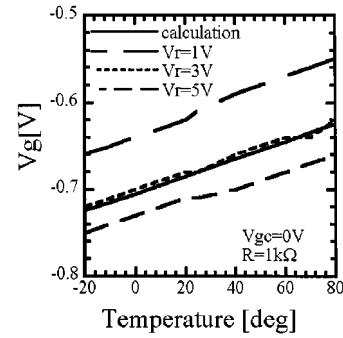

Fig. 4. Calculated and measured  $V_g$  versus temperature characteristics for  $V_r$ .

### B. Design Method

Gate voltage of the temperature-compensation circuit can be calculated from (3). To obtain the ideality factor  $n$  and the Schottky barrier voltage  $\phi_B$  in (3),  $I$ – $V$  characteristics of a GaAs diode with  $S = 150 \mu\text{m}^2$  are measured, as shown in Fig. 3. Here, an  $n$ -type MESFET with the gate length of  $0.5 \mu\text{m}$  and a total gatewidth of  $300 \mu\text{m}$  is employed instead of the diode. The MESFET is connected between the drain and source.  $\phi_B$  and  $n$  are derived from (1) and (2), and are shown as follows:

$$\begin{aligned} \phi_B &= \frac{-kT}{q} \ln \left[ \frac{I_1}{SA^*T^2 \left\{ \exp \left( \frac{qV_1}{nkT} \right) - 1 \right\}} \right] \\ n &\approx \frac{q}{kT} \cdot \frac{V_2 - V_1}{\ln I_2 - \ln I_1}. \end{aligned} \quad (6)$$

$\phi_B$  and  $n$  are calculated as  $1.29$  and  $-0.68 \text{ V}$ , respectively, because the junction size of the diode is  $S = 150 \mu\text{m}^2$ . Fig. 4 shows calculated and measured  $V_g$  versus temperature characteristics.  $V_g$  can be calculated from (3). The calculated and measured results are in good agreement. From Fig. 4, it is confirmed that the gate voltage becomes larger with the temperature increasing and the increasing rate of gate voltage is about  $1 \text{ mV}/\text{C}$  between the temperature range of  $-20^\circ\text{C}$  and  $+80^\circ\text{C}$ .

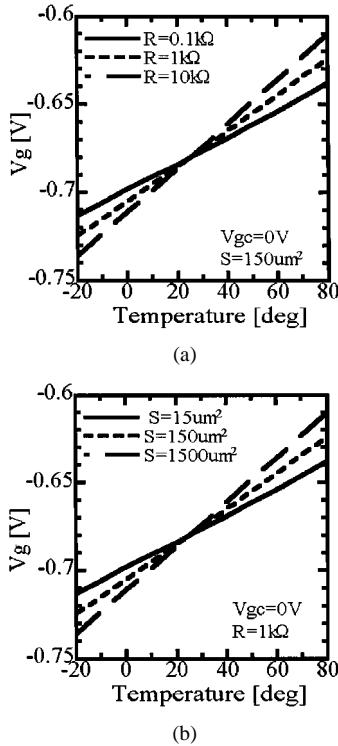

Fig. 5. Calculated  $V_g$  versus temperature characteristics for  $R$  and  $S$ . (a) Variation of  $R$ . (b) Variation of  $S$ .

From the analogy with (5), the following equation is derived for  $\Delta V_g$ :

$$\begin{aligned} \Delta V_g &= \int_{T_l}^{T_h} \lambda \frac{\partial V_g}{\partial T} dT \\ &= \lambda \int_{T_l}^{T_h} \frac{nk}{q} \{ \ln(SRA^*) + 2\ln T + 2 \} dT \quad (7) \end{aligned}$$

where  $\lambda$  is the number of diodes used in series. It is easily considered that a large value for  $\Delta V_g$  can be obtained by using a number of diodes in series.

Fig. 5(a) and (b) demonstrates the calculated  $V_g$  versus temperature characteristics for a variation of  $R$  and variation of  $S$ , respectively. From the figure, it is illustrated that the value of  $\Delta V_g$  increases with the increase of the  $S$  and  $R$ . It is shown that fine adjustment of  $\Delta V_g$  can be obtained by varying  $S$  and  $R$ .

#### IV. APPLICATION TO AN X-BAND POWER AMPLIFIER

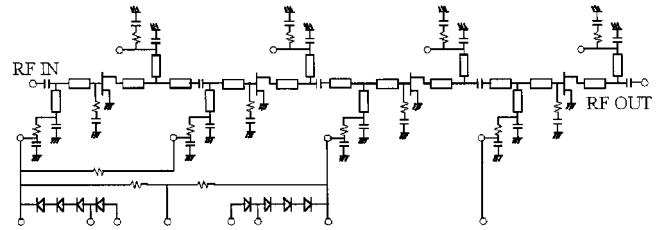

##### A. Design

The presented temperature-compensation circuit is applied to an *X*-band power amplifier. Fig. 6 shows the schematic diagram of a four-stage MMIC amplifier with the on-chip temperature-compensation circuit, which is employed to achieve constant gain performance in the wide temperature range. The required  $\Delta V_g$  is 0.4 V in the temperature range between  $-20^\circ\text{C}$  and  $+70^\circ\text{C}$ , as shown in Fig. 1. The four diodes should be connected in series to achieve  $\Delta V_g = 0.4$  V because the rate of increasing  $V_g$  is about 1 mV/ $^\circ\text{C}$  per one diode, as shown in Fig. 4.

Fig. 6. Schematic diagram of the four-stage MMIC amplifier with the on-chip temperature-compensation circuit.

Fig. 7. Measured small-signal gain as a function of  $V_g$  and temperature of the single-stage amplifier that employs a GaAs MESFET with a gatewidth of 900  $\mu\text{m}$  at  $V_{ds} = 5$  V at the center frequency.

TABLE I

MEASURED FET PERFORMANCES

| $W_g$     | 100 $\mu\text{m}$ | $V_{gss}$           | 18.2 V   |

|-----------|-------------------|---------------------|----------|

| $L_g$     | 0.5 $\mu\text{m}$ | $I_{dss}$           | 30.6 mA  |

| $f_T$     | 20.03 GHz         | $V_p$               | -3.58 V  |

| $f_{max}$ | 17.61 GHz         | $gm(V_g=0\text{V})$ | 10.73 mS |

The measured small-signal gain as a function of  $V_g$  and temperature is shown in Fig. 7. In this figure, the parameter is the gain required for a single amplifier stage. The gain variation of the amplifier can be minimized when  $V_g$  is set along the contour line of equal gain with temperature. The value of  $V_g$  is designed as  $V_g = -3.2$  V at  $25^\circ\text{C}$ . Moreover,  $R$  and  $S$  are designed as  $R = 3\text{k}\Omega$  and  $S = 150\mu\text{m}^2$  to make fine adjustment, respectively. The gain variation is then improved from 2.1 to 0.5 dB, as shown in Fig. 7.

It is required for the MMIC amplifier to achieve both high gain and low power consumption simultaneously. The high-performance MESFET is employed, as shown in Table I. To provide high gain, the amplifier employs a four-stage configuration. Also, to achieve low power consumption, the drain circuit is operated at class AB. Furthermore, to achieve good gain flatness in a broad frequency band, every inter-stage of the MMIC amplifier is matched to achieve good gain flatness in a broad frequency band. The gatewidth of each stage of the FET is chosen to achieve low power consumption.

##### B. Measurement

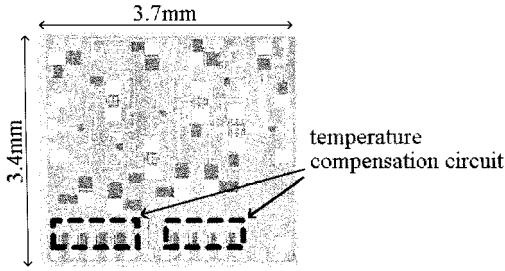

Fig. 8 shows the photograph of the fabricated four-stage *X*-band MMIC amplifier. The temperature-compensation circuit is integrated on the same GaAs chip of the amplifier.

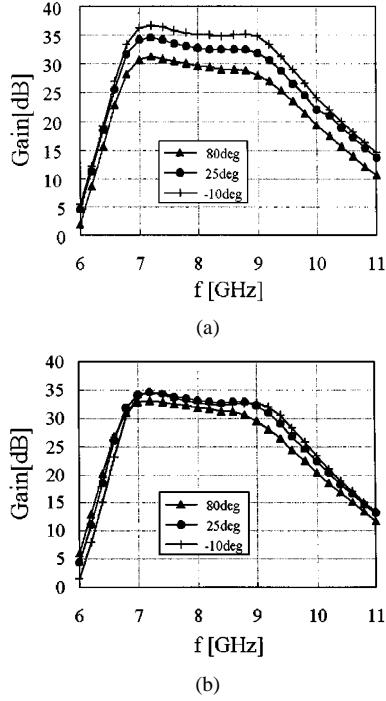

Fig. 9 shows measured frequency characteristics of the small-signal gain of the amplifier without and with the on-chip temperature-compensation circuit at  $-10^\circ\text{C}$ ,  $25^\circ\text{C}$ , and

Fig. 8. Four-stage X-band MMIC amplifier with the temperature-compensation circuit.

Fig. 9. Measured frequency characteristics of small-signal gain of the MMIC amplifier at  $V_{ds} = 5$  V at the total drain current of 79 mA at 25 °C. (a) Without the compensation circuit. (b) With the compensation circuit.

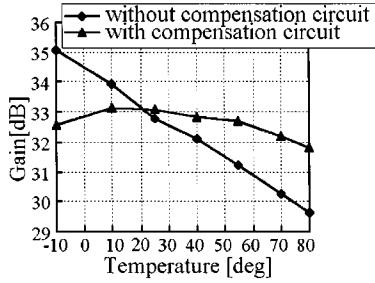

Fig. 10. Measured temperature characteristics of the small-signal gain of the MMIC amplifier at the center frequency at  $V_{ds} = 5$  V at the total drain current of 79 mA at 25 °C.

+80 °C. Fig. 10 shows measured temperature characteristics of the small-signal gain of the amplifier without and with the on-chip temperature-compensation circuit at the center frequency. The amplifier achieves the small-signal gain of 32 dB at 25 °C at the center frequency. It is clearly shown that the gain variation of the MMIC amplifier is improved from 5.5 to 1.3 dB in the temperature range from -10 °C to +80 °C by using the on-chip temperature-compensation circuit.

Fig. 11. Measured temperature characteristics of small-signal gain for six MMIC amplifiers on a wafer at the center frequency at  $V_{ds} = 5$  V at the total drain current of 79 mA at 25 °C.

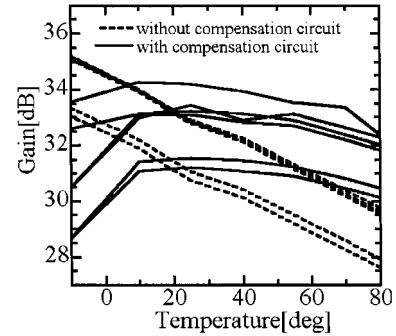

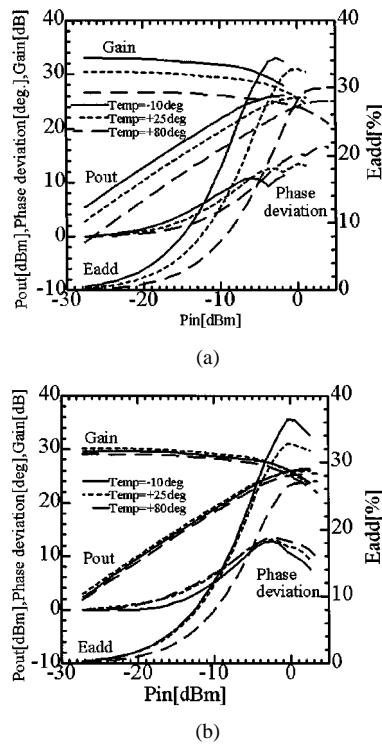

Fig. 12. Measured gain, phase deviation, PAE, and output power of the MMIC amplifier at the center frequency at  $V_{ds} = 5$  V at the total drain current of 79 mA at 25 °C. (a) Without the compensation circuit. (b) With the compensation circuit.

Fig. 11 shows the measured temperature characteristics of the small-signal gain for six MMIC amplifiers on a wafer.  $V_{th}$  of the FET is known to have some variations on a wafer. In order to compress the variation, the gate voltage should be decided to keep the drain current of each FET constant. As shown in Fig. 2, arbitrary  $V_g$  can be achieved by tuning  $V_{gc}$ . The MMICs in Fig. 11 are tuned to the total drain current of 79 mA at 25 °C. Fig. 11 shows that each MMIC improved gain variations with temperature with the temperature-compensation circuit.

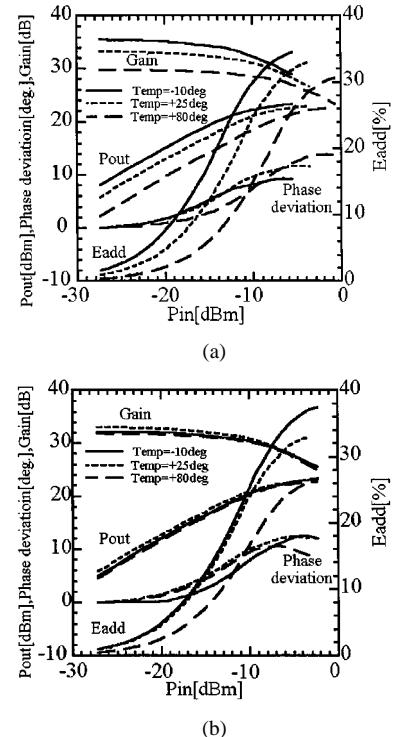

Fig. 12(a) and (b) shows the measured gain, phase deviation, power-added efficiency (PAE), and output power at the center frequency without and with the on-chip temperature-compensation circuit. The variation of gain and output power with temperature is reduced in the wide input power range by using the presented on-chip temperature-compensation circuit.

Fig. 13. Measured gain, phase deviation, PAE, and output power of the amplifier at the center frequency at  $V_{ds} = 7$  V. (a) Without the compensation circuit. (b) With then compensation circuit.

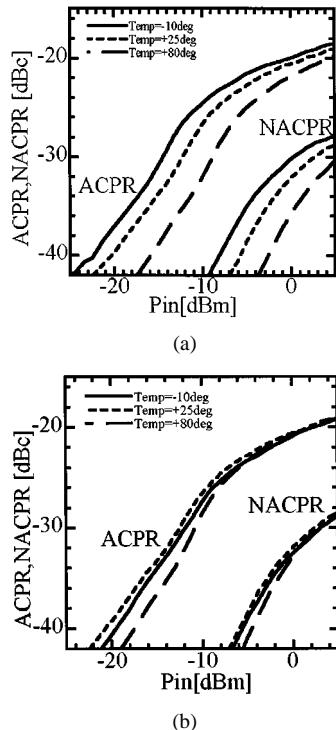

Fig. 14. Measured ACPR and NACPR of the MMIC amplifier at the center frequency at  $V_{ds} = 5$  V at the total drain current of 79 mA at 25 °C. (a) Without the compensation circuit. (b) With the compensation circuit.

The dependence of the improved gain variation with temperature on the drain voltage is now investigated. Fig. 13(a) and (b) shows the measured gain, phase deviation, PAE, and output

power at the center frequency without and with the on-chip temperature-compensation circuit at  $V_{ds} = 7$  V. The gain variation with temperature is improved, as measured at  $V_{ds} = 5$  V. From this figure, the improvement of the gain variation with temperature is not dependent on the drain voltage.

Fig. 14(a) and (b) shows an adjacent channel leakage power ratio (ACPR) and a next adjacent channel leakage power ratio (NACPR) of the amplifier for a 12 Mb/s QPSK modulated signal. The ACPR is measured at 9-MHz offset and the NACPR is measured at 18-MHz offset with a bandwidth of 6 MHz. From this figure, it has been demonstrated that the variations of the ACPR and NACPR are improved with the on-chip temperature-compensation circuit in a wide temperature range. The ACPR is mainly dominated by gain linearity in the developed amplifiers. Gain linearity is determined by output power. Output power keeps constant with the temperature-compensation circuit. Thus, the variation of the ACPR with temperature was improved in a wide temperature range.

## V. CONCLUSIONS

A four-stage  $X$ -band MMIC power amplifier with a simplified on-chip temperature-compensation circuit composed of a few diodes and a resistor has been presented in this paper. The temperature-compensation circuit utilizes the decreasing threshold voltage of the diode with the increase of temperature.

With the temperature-compensation circuit, the gain variation has been improved from 5.5 to 1.3 dB in the temperature range between  $-10$  °C and  $+80$  °C. It has been demonstrated that the presented temperature-compensation circuit is effective for correcting gain variation of a multistage microwave power amplifier in a wide temperature range.

## REFERENCES

- [1] L. Raffaelli and R. Goldwasser, "Temperature compensation for microwave GaAs FET amplifiers," *Microwave J.*, vol. 29, pp. 315–321, May 1986.

- [2] M. Shimada, T. Ohshima, E. Tomita, Y. Ishida, M. Amano, and S. Yamaguchi, "Ka-band 3W SSPA for COMETS," in *Proc. Asia-Pacific Microwave Conf.*, 1994, pp. 647–650.

- [3] V. Alleva and F. Di Paolo, "Temperature compensation circuit for linear microwave amplifier," *IEEE Microwave Guided Wave Lett.*, vol. 6, pp. 238–240, June 1996.

- [4] K. W. Kobayashi, K. MacGowan, R. Kono, and L.-S. Jane Lee, "A monolithic DC temperature compensation bias scheme for multistage HEMT integrated circuits," *IEEE Trans. Microwave Theory Tech.*, vol. 44, pp. 261–268, Feb. 1996.

- [5] K. W. Kobayashi, R. Esfandiari, B. Nelson, K. Minot, W. Jones, M. Biedenender, R. Lai, K. L. Tan, and J. B. Berenz, "A monolithic HEMT regulated self-biases LNA," in *IEEE Microwave Millimeter-Wave Monolithic Circuit Symp. Dig.*, 1994, pp. 121–124.

**Kazuhisa Yamauchi** (M'97) received the B.E. and M.E. degrees in electrical and computer engineering from Yokohama National University, Yokohama, Japan, in 1992 and 1994, respectively.

In 1994, he joined the Mitsubishi Electric Corporation, Kanagawa, Japan, where he has been engaged in research and development of high-power GaAs MMICs and linearizers.

**Yoshitada Iyama** (M'94) was born in Toyama, Japan, on October 24, 1955. He received the B.S., M.S., and Dr.Eng. degrees in electronic engineering from Tohoku University, Sendai, Japan, in 1978, 1980, and 1997, respectively.

In 1980, he joined Kamakura Works, Mitsubishi Electric Corporation, Kamakura, Japan, where he has been engaged in research and development of microwave control circuits and MMICs.

**Mamiko Yamaguchi** received the B.E. degree in physics from the Nara Women's University, Nara, Japan, in 1989.

In 1989, she joined Kitaitami Works, Mitsubishi Electric Corporation, Itami, Japan, where she has been engaged in research and development of GaAs MMICs.

**Yukio Ikeda** (M'97) received the B.S. and M.E. degrees in electric engineering from Keio University, Kanagawa, Japan, in 1979 and 1981, respectively.

In 1981, he joined the Mitsubishi Electric Corporation, Kanagawa, Japan, where he has been engaged in research and development of MMICs and solid-state power amplifiers (SSPAs). He is currently the Team Leader in the Microwave Prototyping Project Group, Information Technology Research and Development Center, Mitsubishi Electric Corporation, Kamakura, Kanagawa, Japan.

**Shuji Urasaki** (M'82-SM'94) received the B.S., M.S., and Ph.D. degrees in electronic engineering from Hokkaido University, Sapporo, Japan, in 1967, 1969, and 1985, respectively.

In 1969, he joined the Mitsubishi Electric Corporation, Tokyo, Japan, where he was involved with antennas for public communications, satellite communications, and radar systems. He is currently the General Manager of the Electro-Optics and Microwave Systems Laboratory, Information Technology Research and Development Center, Mitsubishi Electric Corporation, Kamakura, Japan.

Dr. Urasaki is a member of the Institute of Electronics, Information and Communication Engineers (IEICE), Japan.

**Tadashi Takagi** (M'92) received the B.S. degree in physics from the Tokyo Institute of Technology, Tokyo, Japan, in 1973, and the Ph.D. degree in electronic engineering from Shizuoka University, Shizuoka, Japan, in 1995.

In 1973, he joined the Mitsubishi Electric Corporation, Kamakura, Japan, where he was engaged in research and development of microwave circuits and MMICs and solid-state power amplifiers (SSPAs). He is currently the Project Manager of the Microwave Prototyping Project Group, Information Technology Research and Development Center, Mitsubishi Electric Corporation.

Dr. Takagi is a member of the Institute of Electronics, Information and Communication Engineers (IEICE), Japan.